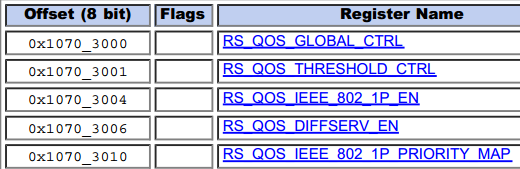

我正在阅读网络处理器 SoC 的数据表。它具有MIPS32 CPU内核和许多集成功能 block 。当我看到这些 block 之一的寄存器映射时,我发现有许多寄存器的大小为 1 或 2 字节:

我一直认为在32位架构中,寄存器大小始终为4字节,寄存器的地址偏移始终为4的倍数。

我是否误解了计算机体系结构的基本概念?

最佳答案

这些是 memory-mapped I/O registers对于 SoC 内置的外设(在本例中为以太网硬件),不是“CPU 寄存器”。

MIPS 具有字节加载/存储指令,因此在这些字节寄存器上使用 MMIO 编写设备驱动程序没有任何障碍。 MIPS's lb instruction将零扩展字节加载到 32 位 CPU 寄存器中。无论您是一次处理一个字符的字符串,还是编写一个使用内存映射字节寄存器与硬件通信的设备驱动程序,都是一样的。

除了为不需要更大的寄存器使用更少的地址空间之外,使用字节寄存器还有一个具体的好处:字加载/存储可以自动访问多个字节 MMIO 寄存器,至少对于 CPU 中断而言。 (即,CPU 不必禁用可抢占式内核设备驱动程序中的中断即可自动修改多个相关寄存器)。

相关:all modern architectures can natively do byte loads/stores 。早期的 Alpha AXP 是最近唯一的异常(exception),它有一个特殊的稀疏 I/O 区域,其中字加载/存储映射到字节加载/存储,因此它仍然可以使用具有一些字节寄存器的普通硬件,而不是只能使用以太网卡设计为仅使用字 I/O 进行编程。

关于cpu-architecture - 为什么 32 位 SoC 的寄存器大小为 1 或 2 字节?,我们在Stack Overflow上找到一个类似的问题: https://stackoverflow.com/questions/48208736/