我很困惑,使用相同 $rt 的 LW 之后的存储字指令如何导致 MIPS 中的管道停顿。 考虑下面的代码块:

lw $s0, 0($t0)

sw $s0, 12($t0)

lw $s1, 4($t0)

sw $s1, 16($t0)

lw $s2, 8($t0)

sw $s2, 20($t0)

这里 3 个单词正在内存中移动。例如,在前 2 行中, $s0 被加载到 , 然后其内容被保存回内存中。我不确定 sw 指令在 EX 阶段还是 MEM 阶段是否需要 $s0 。如果MEM阶段需要的话,不是只要转发就可以解决,不需要停顿管道吗?

最佳答案

假设是的。直接转发到 MEM 阶段将可以连续执行依赖的 LW 和 SW。只要至少由SW存储加载的单词。如果没有管道气泡,SW就不可能使用该加载的字作为地址的基址,否则需要及时转发。

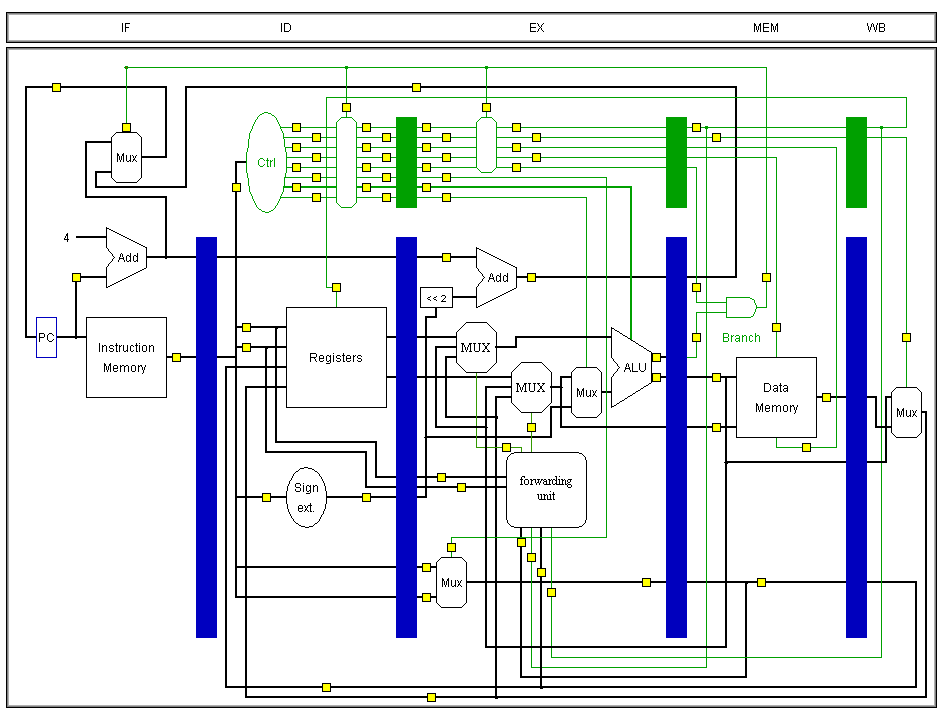

但通常您会看到如下所示的管道(来源:SIM-PL 中的 5 级管道 MIPS 模型),其中只有一个转发器馈入 EX。通过这样的设置,无法从 LW 转发到 SW,因为不存在所需的硬件。

关于MIPS 管道停顿 : SW after LW,我们在Stack Overflow上找到一个类似的问题: https://stackoverflow.com/questions/62117622/