最佳答案

在 RISC-V 中,所有指令必须对齐到 4 字节,但通过允许 16、48 或 64 位指令大小的扩展,允许指令对齐到 2 字节。如规范中所述(V 2.1,第 5 页):

The base RISC-V ISA has fixed-length 32-bit instructions that must be naturally aligned on 32-bit boundaries. However, the standard RISC-V encoding scheme is designed to support ISA extensions with variable-length instructions, where each instruction can be any number of 16-bit instruction parcels in length and parcels are naturally aligned on 16-bit boundaries.

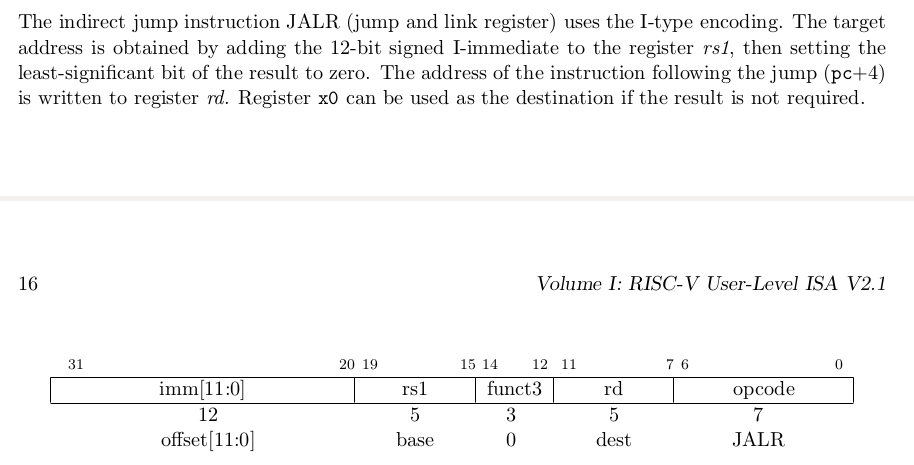

因此 JALR 目标地址中的最低有效位必须始终为零。 RISC-V 的开发人员希望重用现有的格式,而不是创建一种新的格式,即立即数乘以 2。正如第 14 页所解释的那样。规范中16条:

Note that the JALR instruction does not treat the 12-bit immediate as multiples of 2 bytes, unlike the conditional branch instructions. This avoids one more immediate format in hardware.

这并不是一个真正的缺点,因为实现可以使用指针的最低有效位。一个例子是区分函数指针和数据指针,这对于解释器来说很方便。规范中也提到了 p。 16:

[...] allows the low bit of function pointers to be used to store auxiliary information.

关于cpu-architecture - RISC-V : Why set least significant bit to zero in JALR,我们在Stack Overflow上找到一个类似的问题: https://stackoverflow.com/questions/40453719/